Cover Feature: p. 10

How to Simulate Low Voltage, High Power 2000 Amps to a Dynamic Digital Load

**DesignCon Preview: p. 54**

signalintegrityjournal.com

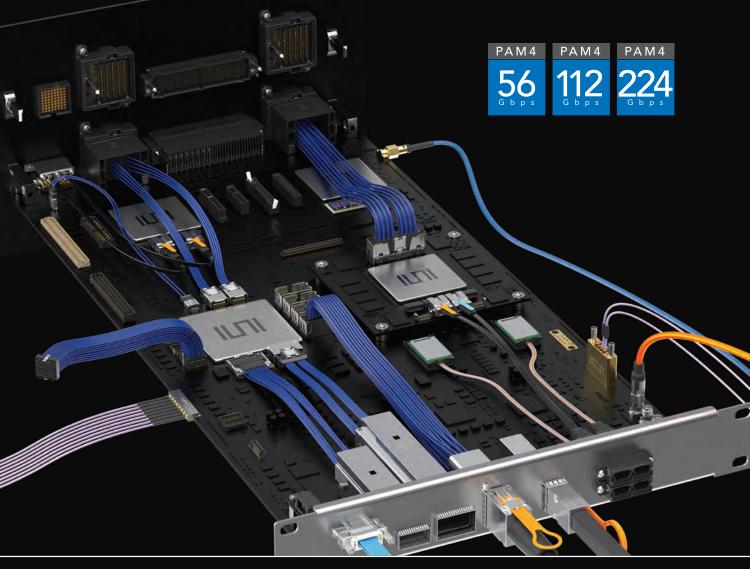

# NEXT GEN CONNECTIVITY FROM SILICON-TO-SILICON™

Samtec's industry-leading signal integrity expertise, full system optimization strategies, and innovative products and technologies help address the challenges of next gen data transmission to 224 Gbps PAM4 and beyond. Learn more at **samtec.com**.

# **TEST & MEASUREMENT PRODUCT GUIDE**

# Available for download and print

Get our new T&M product guide for a complete overview of our portfolio, specifications and product models from Rohde & Schwarz. We offer a broad range of instruments to meet both your everyday needs and your most challenging requirements. Learn more about what's possible when faced with tomorrow's challenges today and prepare for what's next!

# rohde-schwarz.com/discover

**ROHDE & SCHWARZ** Make ideas real

## TABLE OF CONTENTS

#### **Editor's Note**

The Need for Speed and the Cost in Power

Eric Bogatin, Signal Integrity Journal

## **Cover Feature**

How to Simulate Low Voltage, High Power 2000 Amps to a Dynamic Digital Load

Heidi Barnes, Keysight Technologies; Steve Sandler, Picotest; and Benjamin Dannan, Signal Edge Solutions

#### Reflections

**18** Reflections on the Origins of COM **Rich Mellitz, Samtec**

## **Technical Features**

24 Ultrafast Impedance Measurement of Active Ultra-High Current PDNs Steve Sandler, Picotest

# **34** How Interconnects Work: Crosstalk Quantification

Yuriy Shlepnev, Simberian Inc.

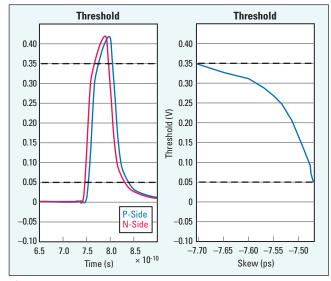

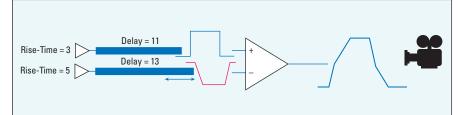

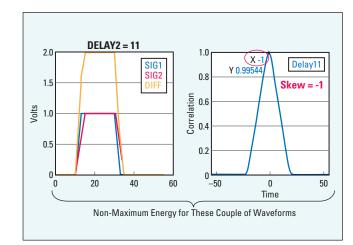

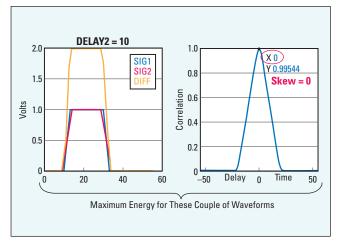

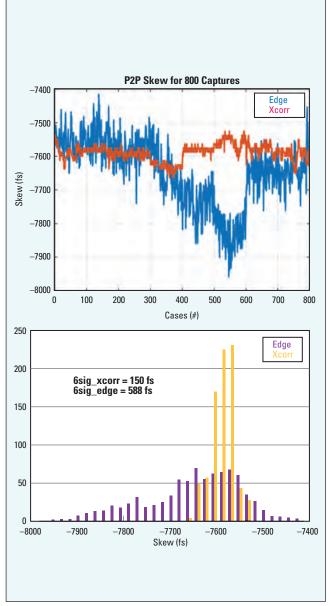

Analysis of Skew

Gustavo Blando and Prashant Pappu, Amazon Web Services

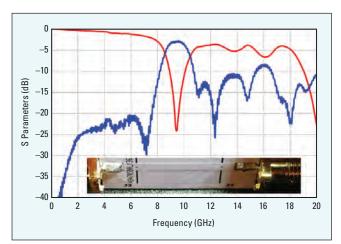

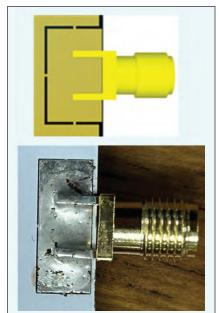

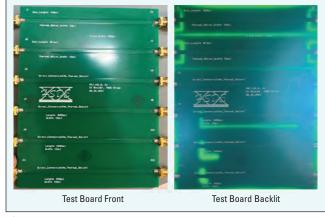

A Subtle Problem to Avoid in Your Next Design

Eric Bogatin, Signal Integrity Journal, and Dheeraj Gooty, University of Colorado Boulder

#### Reflections

Created by Engineers, for Engineers: DesignCon Celebrates 30 Years

Suzanne Deffree, Group Event Director, DesignCon

Follow Us @SIJupdates

Join the Signal & Power Integrity Community

# Staff

Group Director: Carl Sheffres Technical Editor: Eric Bogatin Media Director: Pat Hindle Brand & Content Director: Jennifer DiMarco Editorial & Media Specialist: Kelley Roche Associate Editor: Kaitlyn Joyner Director of Production & Distribution: Edward Kiessling Art Director: Janice Levenson Graphic Designer: Ann Pierce

## CORPORATE STAFF

**CEO:** William M. Bazzy **President:** Ivar Bazzy **Vice President:** Jared Bazzy

#### **Editorial Advisory Board**

Eric Bogatin Benjamin Dannan Jay Diepenbrock Vladimir Dmitriev-Zdorov Jason Ellison Barry Katz HeeSoo Lee Cathy Ye Liu Alfred Neves Istvan Novak Prashant Pappu Steve Sandler Yuriy Shlepnev Bert Simonovich Larry Smith Mark Steffka Michael Violette

# THE SERIAL DATA SUPERPOWER

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 Dur    | TELEDYNE<br>LECROY |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|

| High Definition Oscilloscope<br>2 bit Resolution | Marchen monde blag Band<br>TROBELT I GOSTAL<br>MART E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a 2 Minus d<br>Mart E Rome Inseles 68 8 a | D<br>Pen |                    |

Exceptional Signal Characterization Performance Unrivaled Validation and Debug Capabilities Built-in Serial Data Expertise

# WaveMaster 8000HD

6 GHz – 65 GHz Up to 8 Gpts Capture Memory 12-bit High Definition Oscilloscopes

teledynelecroy.com/wavemaster-hd

# The Need for Speed and the Cost in Power

Eric Bogatin, Technical Editor Signal Integrity Journal

ur economy is both fueled and limited by energy sources. Before the Industrial Revolution, human strength and ability were supplemented by animals. We still retain a measure of power in terms of the ability of a horse. One horsepower (hp) is equivalent to about 750 W(which is about 5x what one percent

750 W, which is about 5x what one person can deliver.

The Industrial Revolution, which began in 1760, was distinguished by the introduction of energy sources that offered even more power than a horse. Initially, power was supplied using wind and water, until the switch was made to steam, wood, coal, and eventually, oil.

However, the transfer of energy from the source to the action was through a mechanical linkage. This meant that the application was always in proximity to the engine. Mills were located next to water sources. Trains carried their fuel and steam engines with them.

Electrification introduced a new era when the conversion of power from its raw source into an easily transportable form allowed the use of the energy remotely. Thomas Edison's first DC power station on Pearl Street in New York City came online in 1882, delivering 100 kW. By 1896, Westinghouse's Niagara Falls AC power station came online, delivering 37 MW of power. The need for electric power was driven by the light bulb and the streetcar. Fast forward to today and the power consumption of the electronics industry. What is fueling this growth is the introduction of artificial intelligence (AI)/machine learning processing in data centers.

According to a report released in 2024 by Newmark, 5% of the data center applications in 2021 were for AI applications. By 2025, 30% of the applications in data centers will be for AI. Capex spending by the companies creating large data centers has a compound annual growth rate of 30%.

Al processing is notoriously power-hungry. The same Newmark report says the typical power consumption of a rack in a data center has been about 12 kW, while an Al processor rack consumes as much as 50 kW.

For example, the NVIDIA H100 GPU has a peak power consumption of 700 W. This is 1 hp of power consumption for one AI processor module. If the rail voltage rail is 1.8 V, this is a current draw of 400 A.

This is roughly equivalent to what an internal combustion car's starter motor draws, which is why battery jumper cables are so thick. A Tesla electric motor only draws 200 A when it is accelerating. Other processor chips are in the same category, drawing 500 to 1000 A, but at lower rail voltages.

The estimated sales volume of the H100 in 2024 is about 2 million units, or about 3.5 million units cumulatively since it was introduced. When all of these processors are operating, the

# RELIABLE ELECTRONIC SOLUTIONS

# SIGNAL

Ethernet, Transceiver Modules, MIL-STD-1553, Data Bus Couplers, Baluns, Delay Lines

# FILTERS

Bandpass, High Pass, Low Pass, Band Reject, Notch, EMI/RFI, Bias Tee, Amplitude Equalizer, Diplexers / Multiplexers

# TRANSFORMERS

Flyback, Buck/Boost, Isolation, Current Sense, Impedance, SMT, THT, MIL-STD-981, MIL-PRF-27

# CAPACITORS

Multilayer Ceramic, Broadband, High Q / Low ESR, Single Layer, High Voltage, Variable, Trimmer, Tantalum

# RESISTORS

Wirewound, Surge, Thin/Thick Film, Carbon Composition, Ressitor Arrays, High Power, Edge Wound Tubular, Metal Film, Microwave

# INDUCTORS

Power, RF, High Frequency, High Q, Military QPL, Medical, Planar, Conical, Ceramic Chip, Toroidal, CMC, THT, SMT, MIL-STD-981, MIL-PRF-27

# INDUSTRIES SERVED

<u>}</u>₽

COMMERCIAL AEROSPACE

MEDICAL

TRANSPORTATION

For more info SCAN HERE! www.inrcore.com/brands/

# SUPPORTING YOUR COMPLETE PRECISION ELECTRONIC COMPONENT NEEDS

# Don't Forget Subscribe/ Renew Today!

signalintegrityjournal.com

#### EDITOR'S NOTE

processors alone will consume 2.5 GW of power, not including the rest of the electronics and their cooling systems. A U.S. household uses about 1 kW of power on average. This is equivalent to the power consumption of 2.5 million households, or the entirety of Los Angeles.

According to the International Energy Agency, in 2022, data centers worldwide consumed a total of 460 Twatt-hours of energy, accounting for 2% of global electricity usage. This is, on average, 40 GW of electric power usage. In the U.S., data centers accounted for about 6% of total power consumption. In Ireland, data centers accounted for 17% of the nation's power usage in 2022. Power usage in data centers is expected to almost double by 2025. This means data centers could account for nearly 10% of the U.S. power consumption within the next few years.

According to the Newmark study, "Energy is the number one challenge for the data center market." It is no wonder that Microsoft, Google, and Amazon have struck deals with operators and developers of nuclear power plants, according to the New York Times. Microsoft was reported to have made a deal to revive the Three Mile Island nuclear plant in Pennsylvania. Amazon and Google have stated that they are considering new, modular nuclear plants, located adjacent to their data centers. Okla, a developer of modular nuclear power plants, signed a 20-year purchase agreement with Wyoming Hyperscale to use Okla's Aurora powerhouse to power new data center campuses.

Just as important to adding to the power grid is reducing the demand for power by more efficient chip design and power delivery. For a 1000 A processor operating at 1 V, the resistive load created by the chip is 1 m $\Omega$ . For the IR losses to be less than 10% of the power consumption, the DC resistance in the power distribution path needs to be less than 100  $\mu\Omega$ . This means more and thicker copper layers and optimal design of the via field from the copper layers to the device being powered. This means measurement capability in the  $\mu\Omega$ range to test the final designs.

The Industrial Revolution began with harnessing power sources that amplified the ability of a person. With today's generation of AI and network processors, one single chip requires 1 hp to operate. The need for speed will be the driving force behind energy production and efforts to make increasingly efficient use of available energy.

#### REFERENCES

"2023 U.S. Data Center Market Overview & Market Clusters," Newmark, January 2024, https://www.nmrk.com/insights/market-report/2023-u-s-datacenter-market-overview-market-clusters.

"Electricity 2024, Analysis and Forecast to 2026," International Energy Agency, January 2024, https://iea.blob.core.windows.net/assets/6b2fd954-2017-408e-bf08-952fdd62118a/Electricity2024-Analysisandforecastto2026. pdf.

HYPERLABS HAS BEEN INNOVATING ULTRA-BROADBAND PRODUCTS TO 110GHz AND BEYOND, SINCE 1992.

AMPLIFIERS, BALUNS, POWER DIVIDERS, DC BLOCKS, BIAS TEES, PICKOFF TEES, AND SO MUCH MORE...

WE FOCUS ON OPTIMAL SIGNAL INTEGRITY TO HELP YOU MAINTAIN THOSE CLEAN EYES THAT YOU'VE WORKED SO HARD TO CREATE...

**COME SEE WHAT'S NEW AT DESIGNCON BOOTH No. 1055**

www.HYPERLABS.com +1.720.497.6538

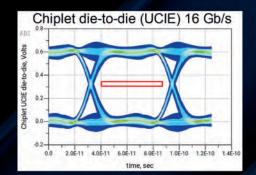

# How to Simulate Low Voltage, High Power 2000 Amps to a Dynamic Digital Load

Heidi Barnes, Keysight Technologies; Steve Sandler, Picotest; and Benjamin Dannan, Signal Edge Solutions

ardware engineers are learning the hard way that power integrity (PI) requires electromagnetic (EM) simulation of the printed circuit board (PCB) power delivery network (PDN). Traditional rules-of-thumb and leveraging data sheet examples are not an option as designs move from hundreds of Amps (A) to thousands. 1000 A across a 100 microhm ( $\mu\Omega$ ) PCB PDN is still 100 millivolts (mV) of IR drop and 100 Watts (W) of

power dissipating as heat. This is one of the fundamental reasons for transporting power at a higher voltage and lower current for as far as possible. Less power lost in the path to the load. The other reason is impedance. Power rail voltage ripple is a direct result of dynamic di/dt currents interacting with the path impedance. When currents go up, the target impedance must go down to keep power rail voltage ripple within specified limits. Controlling the power delivery DC resistance and the parasitic path inductances

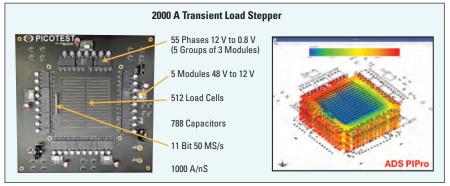

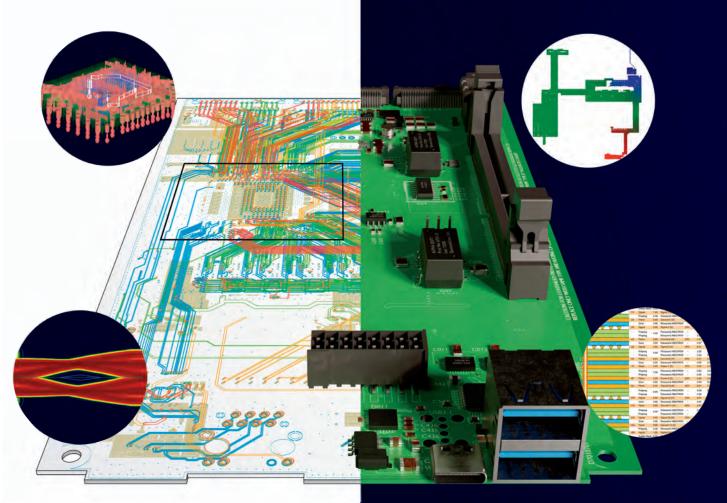

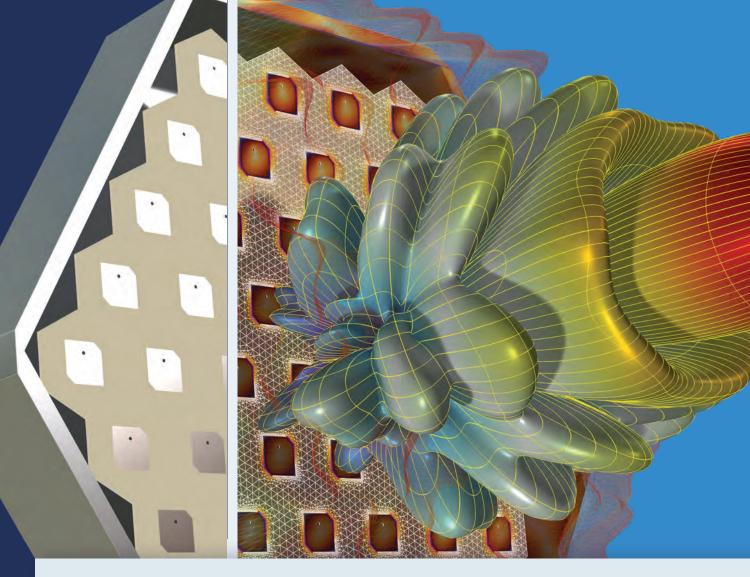

▲ Fig. I A topside picture of the Picotest 2000 A transient load stepper PCB is shown on the left. The PCB CAD data is imported into a full 3D-EM simulator to validate DC, electrothermal, and AC impedance performance.

of the PCB is a critical part of creating a Digital Twin model for designing a 2000 A PDN for a dynamic digital load.

**Figure 1** shows an example of a 2000 A PDN design that Picotest uses to demonstrate their 2000 A 11-bit programmable transient load stepper.<sup>1</sup> This design was imported into a 3D-EM simulator to validate DC, electrothermal, and AC impedance design performance.

#### WHAT IS DRIVING THE NEED FOR A PCB PDN EM MODEL?

To explain why the impedance of a 2000 A PDN is orders of magnitude harder than expected, one can combine the traditional target impedance equation with the need to minimize power. The PI engineer defines a target impedance so that a di/dt at any frequency, DC to GHz, will not result in exceeding the maximum allowed voltage ripple. The equation for target impedance is simply the maximum delta allowed voltage ripple divided by the worst case dynamic delta current change, as shown in Equation 1.

$$Z_{Target} = \frac{\Delta V_{Max\,Ripple}}{\Delta I_{Max\,Transient\,Load}} \tag{1}$$

Combining this equation with the maximum available power provides an interesting look at the challenge PI engineers are facing. The relation between power and current can be estimated by the ideal DC-DC converter equation, where power in equals the power out, as shown in Equation 2:

$$P = V_{in} \times I_{in} = DV_{in} \times \frac{1}{D}I_{in} \quad (2)$$

where D is the duty cycle of the DC-DC regulator.

Here, D is less than or equal to 1, and shows how the current can be proportionally increased as the voltage is decreased with a point-of-load DC-DC converter while maintaining the same power level. If the allowed voltage ripple is set to 5% and the maximum delta current transient to 50% of the maximum current, then Equation 3 can estimate  $Z_{\text{Target}} = \frac{D \times V_{\text{in}} \times 5\%}{1 \times 10^{-500}}$

$$\frac{1}{D} \times I_{in\_max} \times 50\%$$

$$= D^2 \frac{V_{in}}{I_{in\_max}} \times 10\%$$

$$= \frac{(D \times V_{in})^2}{P_{max}} \times 10\%$$

(3)

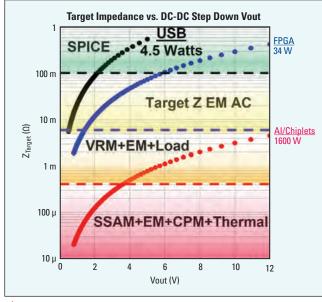

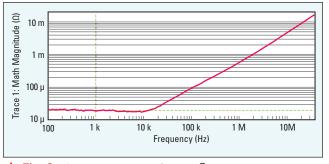

Plotting  $Z_{Target}$  as a function of the DC/DC converter output voltage,  $D \times V_{in}$ , while holding the power constant for a given application shows an exponential decrease in target impedance, shown in **Figure 2**. A USB design at 4.5 W and 5 Volts

▲ Fig. 2 A plot showing how target impedance decreases with the output voltage of a DC-DC regulator for a given application where the power is held constant. As the output voltage drops the current increases proportionally, but the target impedance decreases exponentially.

## COVER FEATURE

(V) has a target design impedance in the hundreds of milliohms (m $\Omega$ ) and may not be impacted by PCB PDN path parasitics; however, if the voltage is dropped down to sub-1 V levels, then  $Z_{\text{Target}}$  can easily drop into tens of m $\Omega$ . Typical FPGA designs at around 34 W with a 12 V input power connector to the PCB quickly drop to a  $Z_{\underline{Target}}$  of a few m $\Omega$  for the sub 1 V core power rail. Finally, for the new generation of AI and cloud compute chips running at 1600 W, the target impedance at 12 V is already a challenge at 1 mΩ levels. This helps to explain why 48 V power rails and higher are now showing up in electronic designs to reduce the impact of PCB path parasitics until the final pointof-load DC-DC conversion, where the 2000 A is needed. Running 1600 W on a sub-1 V power rail drops the design target impedance into the tens of μΩ.

Historically, SPICE simulations without PCB EM models have been used for designs above 100 m $\Omega$ . The concept of Z<sub>target</sub> and the need to include the PCB parasitics as an EM model became necessary as target impedances decreased to tens of m $\Omega$ . A typical PCB PDN with 5 cm between the voltage regulator module (VRM) and the load can easily have m $\Omega$  of DC path resistance and hundreds of pHs of inductance that can no longer be considered small in proportion to Z<sub>Target</sub>. As Z<sub>Target</sub> decreases from m $\Omega$  to  $\mu\Omega$ , there is also an increasing demand for higher fidelity Digital Twin PDN simulations that include VRM behavioral models and worst case dynamic loads.<sup>2</sup>

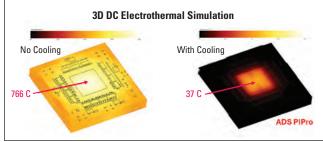

#### HOW TO CREATE THE PCB PDN EM MODEL

Knowing that PCB EM parasitics are a critical part of designing a 2000 A power delivery network, the next question is how to create and use a PCB PDN EM model in a simulation. EM simulator tools like Keysight's ADS with PIPro EM are optimized for multi-layer laminate PCB PDN simulations. The designs are imported from fabrication files like ODB++<sup>TM</sup> and IPC-2581<sup>TM</sup> with access to components, net names, and PCB stackups that allow for an increased level of automation when setting up a full 3D-EM analysis. EM models are needed for DC IR drop, DC Electrothermal, and AC impedance. DC IR drop models can quickly identify any asymmetries in the voltage delivery to large digital loads with hundreds of power and ground pins. Optimum locations for sense lines can be found, and layouts modified to maximize the unitormity of the power delivery. DC electrothermal simulations can help determine the amount of cooling required and the trade-offs between thicker copper layers versus adding more layers to prevent thermal run away and improve reliability (see Figure 3).<sup>1</sup>

AC Impedance EM models are a critical part

### COVER FEATURE

▲ Fig. 3 DC electrothermal simulation of the Picotest 2000 A transient load stepper showing the importance of water cooling to prevent thermal runaway.

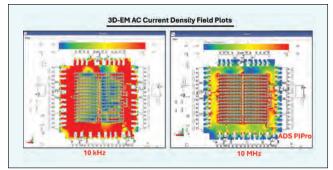

▲ Fig. 4 The 3D EM AC current density plots for the Picotest 2000 A transient load stepper show how the current delivery changes from the VRMs at 10 kHz to the decoupling capacitors under the load cells at 10 MHz.

of the Digital Twin PDN model that can simulate transient behavior to validate the pass/fail ripple voltages on the power rail. The PCB AC Impedance EM model can also be used to look at the spatial distribution of current densities over frequencies. The current density plots in **Figure 4** show how the VRMs deliver power from the edges at low frequency, while the decoupling capacitors under the 512 load cells dominate at 10 MHz.

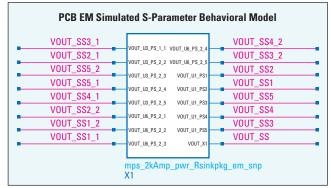

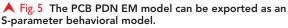

The AC impedance model includes ports for the decoupling capacitors so values can be optimized to meet a desired  $Z_{Target}$  in the frequency domain. This decoupling capacitor optimization is best done before adding the EM model to the end-to-end PI Digital Twin simulation. To use the AC Impedance EM model in a PI Digital Twin simulation, it can be saved as an S-parameter behavioral model, as shown in **Figure 5**, with connecting ports to the VRM, the load, and passive components, such as decoupling capacitors.<sup>1</sup>

# HOW TO CREATE THE SWITCHING VRM MODEL AND TRANSIENT LOAD

The PI Digital Twin connection to the VRM needs to be a behavioral model of the VRM that can handle the large signal dynamic behavior of the DC-DC converter's interaction with the load. Complete transistor level models of a VRM may work for evaluating set point characteristics, but when connected to real-world PCB EM models and dynamic loads, a transistor level simulation can fail to converge or

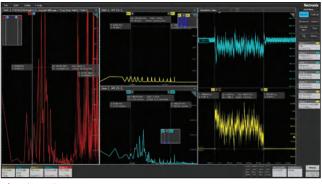

▲ Fig. 6 The plots on the top show how a transient simulator must wait to reach steady state before the voltage ripple can be measured, while the bottom plots show how HB can simulate enough harmonics of the switching frequency to directly convert to the steady state voltage ripple solution.

# Have you tried our MAGPrp<sup>™</sup> Common Mode Choke Finder?

# There's nothing common about it!

# Find the optimal off-the-shelf common mode chokes for your EMI/RFI filter parameters.

**Step 1:** Search parts by your desired Impedance, Attenuation or Inductance at your operating frequency.

**Step 2:** View results in a sortable table with complete performance specifications and select parts for further analysis.

**Step 3:** Quickly compare impedance and attenuation vs. frequency graphs for up to six part numbers.

**Step 4:** Request free samples of the most interesting parts for evaluation and testing.

# It's that Simple!

Try it at **coilcraft.com/CMCfinder**.

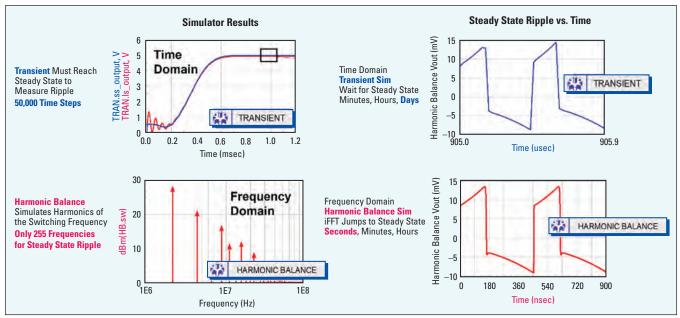

▲ Fig. 7 The modular design of the off-the-shelf VRMs allows paralleling the output phase to get to 2000 A. In simulation, all the phases are using the same VRM SSAM model.

▲ Fig.8 The end-to-end PI PDN Digital Twin with 55 VRM phases switching at 500 kHz, connected to a PCB PDN EM model, and a transient 91 kHz switching load. The circuit uses an S-parameter simulator for PDN impedances and HB for steady state large signal transient ripple.

take days to run. To get around this problem, the Sandler state-space-average (SSAM) VRM behavioral model can be used.<sup>3</sup> This model captures the classic behavior of a switched mode power supply design including the feedback characteristics to create both small signal AC behavior and large signal switching transients. The reason for this type of behavioral model is that it can be run both in a traditional transient SPICE simulation, or in the frequency domain using harmonic balance (HB). HB is a powerful technique that simulates a circuit with enough harmonics of the fundamental frequency to convert the spectral data to the time domain using an iFFT. The benefit is that the HB simulation jumps directly to the steady state condition and avoids the longer simulation times required for a transient simulation to reach steady state. Running the switching model in both a transient SPICE simulator and the HB simulator shows that they get the same result (see Figure 6).4

This SSAM VRM model can easily be paralleled together to represent the 55 phases of the VRMs each delivering ~36 A to reach a total of 2000 A

for the Picotest 2000 A transient load stepper design (see **Figure 7**).

The last step in creating the Digital Twin is to add the behavior of the load. This can include the passive S-parameter behavioral model of the package die PDN and a dynamic current I(t) of the load. Here, a switch model that can run in transient or HB is once again used to create a switching transient load at the desired frequency.<sup>1</sup>

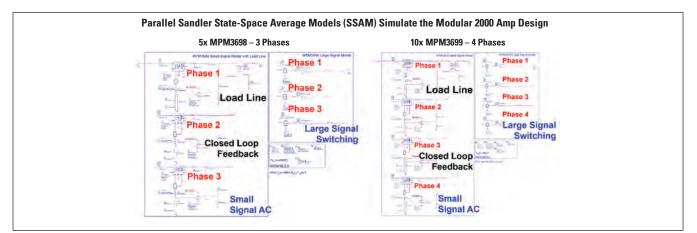

## THE COMPLETE PI PDN DIGITAL TWIN

The complete 2000 A PI Digital Twin model is shown in **Figure 8**. The PCB EM model connected to the dynamic load is replicated twice; one is connected to the small signal AC output from the SSAM, and the other is connected to the SSAM large signal switching output. A third path with just the PCB EM model is also added to provide impedance information.

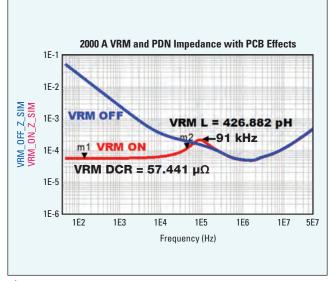

Simulating just the impedance helps to identify resonances with higher impedance that can lead to worst case power rail ripple if excited with a dynamic load. In this design, there is a peak in the

# Siglent Delivers 12-Bit Oscilloscopes to address Signal Fidelity Challenges on every bench

Every Bench. Every Engineer. Every Day. support@siglentna.com www.siglentna.com

▲ Fig. 9 Simulating the PI Digital Twin in the frequency domain with the VRM on and off shows how the VRM controls the impedance below 30 MHz, and at 91 kHz there is an impedance peak indicating a resonance in the PDN.

impedance around 91 kHz (see **Figure 9**). This resonance is a result of higher than desired output impedance from the VRMs, and a limited amount of bulk capacitance. The desire was to push the performance of the VRM technology instead of spending more money and space for the bulk capacitors in this initial demonstration of the Picotest 2000 A transient load stepper.<sup>1</sup>

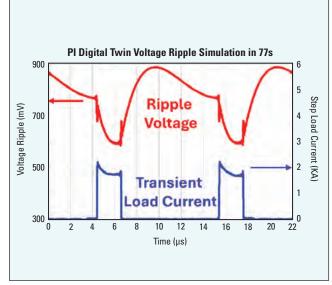

Knowing that a dynamic load switching at 91 kHz can excite this resonance and cause a worst case voltage ripple, the 2000 A PDN Digital Twin is then run with this worst case 2000 A load being turned on and off at 91 kHz.<sup>2</sup> The 55 phases of the VRMs are all switching at 500 kHz with different phases to deliver the dynamic 2000 A current to the 91 kHz load. The HB simulator runs this full PI Digital Twin simulation in less than 77 seconds (see **Figure 10**).

The PI Digital Twin shows the corresponding undershoot (droop) and overshoot (kick) that occurs with the 2000 A load. Making design modifications with the PI Digital Twin that simulates in 77 seconds can build engineering intuition, save hours of engineering debug time on the bench, and mitigate expensive hardware failures.

## **CONCLUSION**

Including the EM behavioral model of the PCB PDN parasitics is now a critical part of designing and validating a 2000 A PDN. The orders of magnitude drop in  $Z_{\text{target}}$  from hundreds of m $\Omega$  to tens of  $\mu\Omega$  is driving the need for higher fidelity PI PDN Digital Twin simulations that include a dynamic switching VRM model, the PCB PDN EM model, and a worst case transient load model to validate the design before fabrication. Behavioral VRM models

▲ Fig. 10 The PI PDN Digital Twin simulates in 77s with all 55 phases of the VRMs switching at 500 kHz and the 2000 A transient load switching at 91 kHz.

like the Sandler SSAM and transient load switch models that run in HB have a significant simulation time savings advantage by jumping directly to the steady state results for fast optimization and debugging of a design. Digital Twin HB simulations can run in a matter of seconds or minutes compared to transient simulations, which can take hours or even days when including the PCB EM model. Creating the PCB PDN EM model also continues to get easier. EM simulators that are optimized for PCB PDN simulations provide an increased level of automation to enable the basics of DC IR Drop, electrothermal, and AC impedance for early detection of design issues. The ability to optimize a PDN for  $Z_{\ensuremath{\text{Target}}}$  with PCB parasitics in the frequency domain and to then export to an end-to-end PI Digital Twin simulation for validation in the time domain should be standard practice for the PI engineer.

#### ACKNOWLEDGEMENTS

A special thanks to the Research and Development team that keeps advancing the EDA simulation technology, John C. Moore, Robin Sercu, Marnik Brunfaut, Tim Boonen, Marwan Antoun, Oleh Kozynets, Hyoung Min Suh, Jan Vanhese, and Bram de Greve. A special thanks to Emma Duhrssen for keeping track of all the hardware pieces and enabling great things to happen.

#### REFERENCES

- S. M. Sandler, B. Dannan, H. Barnes, I. Ben Ezra, and Y. Ni, "Design, Simulation, and Validation Challenges of a Scalable 2000 Amp Core Power Rail," *DesignCon 2024*.

- H. Barnes, J. Carrel, and S. Sandler, "A Method for Dynamic Load Current Testing with a Benchtop Power Supply," *DesignCon 2020*.

- 3. S. M. Sandler, "Measurement Based VRM Modeling," IEEE SPI 2017.

- S. M. Sandler, B. Dannan, H. Barnes, and C. Yots, "VRM Modeling and Stability Analysis for the Power Integrity Engineer," *DesignCon*, 2023.

# **Reflow Stable Multiport PCB Connectors**

# Maintains Physical and Electrical Integrity During Solder Reflow

- Capable of withstanding up to 500 °C

- Dimensionally stable during solder reflow

- 2 or 4 port configurations

- Capable of multiple reflow cycles

# **Reflections on the Origins of COM**

## **Rich Mellitz, Samtec**

Channel operating margin (COM) is a well-documented IEEE standard that has been used successfully since 2014 in the design of channels and specification of interconnect. The goal of this article is not to explain what COM is, or how it works (see the reference section for this information). Rather, this article reflects on the COM origin story as recalled by Rich Mellitz, who was in the room when the need for something like COM was realized, and who was one of the chief architects of the spec. The following aims to capture the story of the creation of the COM standard in the words of Mellitz, as well as its evolution and where it might be headed next.

ome would argue that it all began in the 1990s with the needs of PCI Express®, InfiniBand™, 10 Gbps Ethernet,<sup>1</sup> and when semiconductor companies had to specify electrical channels. These electrical channels use separate differential pairs for transmit and receive. Here, the term "line" is intended to mean one transmit to receive differential pair.

Before getting too far into the story of COM, it might be best to also define what is meant by data rate. IEEE specifies the delivered data rate for a MAC. For example, 10 Gbps Ethernet<sup>1</sup> was really 10 Gbps Ethernet on four pairs of twinaxial cabling. In other words, 2.5 Gbps per line. However, since the data was 8B10B NRZ encoded, the actual line rate was 3.125 Gbps. Thus, the Nyquist rate is 1.5625 GHz. This is different from PCIe, OIF, and InfiniBand, where the data rate is actual symbol transfer rate per line. For convenience, one can simply refer to 25 Gbps, 50 Gbps, 100 Gbps, 200 Gbps, and 400 Gbps per line without detailing the actual data rate load for encoding.

# Identifying the Problem (1990-2010)

In the 1990s, copper electrical bus rates were mostly under a gigahertz. Losses and crosstalk below a gigahertz are generally considered "well behaved" because the electrical wavelengths are on the order of PCB design sizes. At this time, it was sufficient for many semiconductor manufacturers to have rudimentary channel requirements based on characteristics described as simple functions of frequency. Eye diagrams emerged for compliance testing, augmenting the typical test method of the time:

set up and hold timing verification.

Around 2002, IEEE's Ethernet broke the 10 Gbps barrier, which led to other 10 Gbps projects, such as IEEE Std 802.3ap-2007<sup>2</sup>, where 10 Gbps per line interconnect channels were defined for a backplane and data center twinaxial cabling. The focus for the 10 Gbps copper backplane and cable project was frequency domain (FD) limit masks to support a 1-m backplane reach objective. Although this was sufficient for interconnect designers of the time, unfortunately, the interaction between these masks and transceiver specifications was somewhat weak.

In 2010, the IEEE project IEEE Std 802.3ba-2010<sup>3</sup> extended inter-box cabling to 7 m of electrical cable using the same 10 Gbps FD masks for electrical channel compliance. 2012 showed a push for 25 Gbps per line as the IEEE 100 Gbps Backplane and Copper Study Group<sup>4</sup> kicked off. Electrical lengths of concern shrank to about an inch as a result of the 25 Gbps per line signaling. This broke the FD mask paradigm because in order to make channel compliance work, too much guard band would be needed. Essentially, there was no easy way to budget between insertion loss, crosstalk, return loss, and transceiver capability. This need paved the way for COM.

Very quickly, it was discovered that relying on maximum insertion loss was not sufficient. It was also realized that insertion loss curves near 13 GHz were not smooth. The aberrations around a fitted, smooth, insertion loss curve were called insertion loss deviation (ILD). More ILD meant less margin. What caused this was that via/connector/package geometries and the spacing between them were approaching the critical electrical lengths. This resulted in reflection starting at 5 GHz. It was known that more reflection caused more ripple in the insertion loss curve, and semiconductor manufacturers indicated this would result in lower performance. The frequencies of interconnect impairments also spawned conversation contrasting NRZ and PAM4. Although NRZ dominated 25 Gbps designs, the 50 Gbps line rate favored PAM4.

Crosstalk was another issue addressed during the 10 Gbps per line project.<sup>2</sup> Crosstalk was converted to a single RMS voltage, called integrated crosstalk noise (ICN), which is computed with the normalized integration of the power sum of all frequencies in the crosstalk responses. (Recall Parseval's theorem, which states that total power in the time domain is the same as total power in the FD.) In addition, insertion loss to crosstalk ratio (ICR) was borrowed from J. Salz's work,<sup>5</sup> supporting the notion of a budget between crosstalk and insertion loss.

At around the same time, some people were having discussions about how to determine a maximum channel capability based upon the Salz limit.<sup>5</sup> This tactic had been used for the higher power, lower radix "BaseT" standards. The assumption is that transceivers have at their disposal unlimited DFE and FFE. Data center switch and network cards require orders of magnitude less power per line and have an order of magnitude higher radix and density. The Salz limit was interesting, but required too much power for the backplane application. So, the industry ended up focusing on ILD and ICR, as these were the things that were important for physical design.

In 2010, there was still no standard method or simulation to evaluate performance. Specifically, there was a lack of signal integrity simulation standardization. The result was that standards development was relegated to what could be called the "ouch test." The interconnect designers would create BGA ball to BGA ball models called channels, and transceiver vendors would say "ouch" when the channel was too tough or not working in a lab experiment. For standards development, deciding on channel and transceiver parameters was kind of like playing poker. Unfortunately, at the time, there was a significant disconnect between physical design and what the simulations could provide.

During this time, interconnect designers seemed happy using insertion loss, return loss, crosstalk, and ICR curves, gaining apparent performance by minimizing ICN and ILD for design. Unfortunately, the FD bounds, while good for interconnect designers, were of limited use for transceiver designers. Consider that the 10 Gbps backplane ILD mask was reasonable for the physical design of data center switches and servers. The original expectation was that five DFE taps would handle the data center designs like IBM's Blade Center. The disconnect was that the actual designs requited up to 50 DFE taps. Moving to 25 Gbps per lane (25G), it was realized that a linkage was needed between the physical channel design and transceiver or SerDes design. The two spoke different languages. This growing need for a "Rosetta Stone" paved the way for something like COM.

## COM Evolution (2011-Present)

Interconnect designers require a budget that includes insertion loss, crosstalk, and reflections. However, consideration of SerDes needs must also be part of this budget. Around 2010-2011, the group was working on projects for 25G and started to experiment with post processed FD metrics graduating to including a "dibit" time domain response suggested by Charles Moore.<sup>6</sup> The method was mostly based on power losses, but did not have direct linkage to the time sampled SerDes. This opened the door to time domain.

Early in the 25G project, the group started examining the channel pulse response. A data stream is made up of a pulse response convolved with a symbol stream. A pulse response was recognized as perhaps the lynchpin that would connect the SerDes designer and interconnect designer. Many published works suggested that a SerDes architect could translate pulse responses into design capability. Anecdotally, interconnect designers can see direct effects of features that resulted from loss, reflection, and crosstalk.

Prior to the COM proposal, there was a lot of angst about converting S-parameter measurements made in the FD into a pulse response in the time domain. Determining a pulse response is somewhat easier if a transmitter filter, receiver filter, and a pulse response filter are applied before converting the S-parameter into a pulse response using an FFT.

#### REFLECTIONS

At that time, SiSoft (now part of MathWorks) had a proprietary way to create a pulse response from FD S-parameters, and SiSoft employees were active in the IEEE meetings. Walter Katz (SiSoft) favorably correlated pulse responses, which they compared to the pulse responses for a filtered FFT method were considered for COM.<sup>7</sup> This is when things started to get interesting. The turning point was moving discussions to pulse response analysis.

Pulse responses sampled at one symbol interval correlate to one unit interval (UI) spaced samples in a data stream waveform (because of linear time invariance and convolution). For these purposes, UI corresponded to the time between symbol samples. The RMS of the data waveform sampled at one UI represents voltage average power. The same voltage average power could be determined by taking the root of sum of the squares (RSS) of the samples in the pulse (as long as the data was somewhat random). An inter-symbol interference (ISI) noise vector was created by not including the sample at the pulse peak. Since crosstalk is all noise, the entire sampled crosstalk pulse response was used as noise. There was now a way to combine crosstalk with reflections, and then compare them to pulse peak (which would be proportional to insertion loss).

Next, the group began to discuss cursors, which refer to samples of the victim response space at one UI. The peak sample index is cursor 0. Samples before would be negative cursors and samples after would be positive cursors.

The industry needed to move to the statistical domain. The RSS for samples of a pulse response is ISI. It corresponds to the RMS of respective sampled noise of the random data response. RMS noise can be considered a normal or Gaussian distribution. Enter the statistics of noise. The group talked about voltage of noise at certain probability, such as a probability of 1e-12 corresponds to  $\pm 7$  sigma where sigma is the RMS. Much discussion ensued about whether the assumption of Gaussian noise was overly pessimistic for copper channels.

During the same era, other standard groups addressed the issues of expected noise. Work on PCI Express Generation 1 and 2 and SAS/SATA, for example, centered around data patterns that created the worst-case ISI or noise. This concept was called peak distortion. The objective in the IEEE project was to address the ISI that corresponded to a line error rate of close to 1e-12. The worst-case ISI error rate is typically many orders of magnitude lower. Conversations started by aligning samples to the pulse peak. The group addressed actual clock and data recovery sampling much later. The sum of the magnitude of the 40 worst UI spaced samples in the pulse response would seem to correspond to probability of 1e-12.

What was significant here was the whole no-

tion of doing statistical analysis with crosstalk. What are the statistics that should be used? Should the industry just use RMS values for everything? One of the discoveries during this process was that, when using statistical Gaussian noise assumptions for the noise one gets in backplanes and cables, one ends up completely over designing.<sup>8</sup> In other words, one overpredicts the noise by quite a bit as required by a maximum bit error ratio. That did not sit well, so the group decided to use what was considered to be the "real" noise profiles that are generated. This was the point when COM could take advantage of the actual nature of electrical channels. Actual electrical crosstalk and ISI noise distributions were not independent and identically distributed (IID) random processes.

Then, a curious thing happened. People started publishing their interconnect models. The IEEE working groups became a public repository for channel models that were representative of interconnects being produced, including backplanes and cables. In the past, someone might show you a picture and graphs of their interconnect. But once 25 Gbps was reached, everyone realized it was a way to manage the standard process by using channel S-parameter models of what the industry might be doing or planning. This became even more prolific at 50 Gbps. These models are a management tool for standards development. The other half is managing transmit and receive parameters, which were embodied as COM parameter tables to be incorporated into the standard.

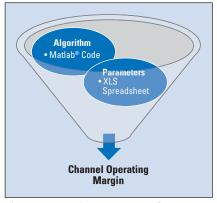

COM was proposed in 2012 for a channel compliance method<sup>9</sup>, which included the IID nature of interconnect and minimum transceiver capability. Transceiver capability is embodied in the tables within the standard. COM is a documented algorithm in IEEE802.3 and it is NRZ and PAM4 capable. An evolutionary MATLAB example script was used throughout all the projects which used COM (see **Figure 1**). Although not a standard compliance, the script proved useful to move the wave of standards development.

Parameters are represented in a spreadsheet which the MAT-LAB script uses to statistically evaluate electrical S-parameter channel models using an algorithm procedure described in Annex 93A and presently for 200 Gbps An-

▲ Fig. 1 Implementation of COM.

e no-

# Trusted Next-Generation Testing High Performance BERT

# Signal Quality Analyzer-R MP1900A

Anritsu's Signal Quality Analyzer-R MP1900A is an all-in-one high-performance multi-channel BERT with 8 slots for expansion modules such as 128Gbps PAM4 Pulse Pattern Generator, 118Gbps PAM4 Error Detector, and Jitter/Noise Generator. The MP1900A expands measurement applications supporting signal integrity analyses of high-speed network interfaces such as with 200GbE/400GbE/800GbE standards. In addition, the MP1900A has built-in Link Training/LTSSM analysis function supporting high-speed serial bus interfaces such as PCI Express and USB.

Scan the code to learn more about our **Next Generation Signal Integrity Testing Solutions** and explore the Anritsu Digital and Optical Testing Solutions Resource Center.

#### REFLECTIONS

nex 178A of the IEEE 802.3 Ethernet standards. Moving forward, there are plans to incorporate the MATLAB COM script and associated spreadsheets in an IEEE SA Open Source under an IEEE802.3 umbrella, which will lead to a new COM evolution.

Since its inception as part of the 802.3bj project, COM has undergone many revisions based upon industry needs and changing market potential. It has been adopted for other IEEE projects such as IEEE Std 802.3bm-2015,<sup>10</sup> IEEE Std 802.3by-2016,<sup>11</sup> IEEE Std 802.3bs-2017,<sup>12</sup> IEEE Std 802.3cd-2018,<sup>13</sup> IEEE Std 802.3ck-2022,<sup>14</sup> IEEE Std 802.3df-2024,<sup>15</sup> and IEEE P802.3dj.<sup>16</sup> In addition, COM has been borrowed for OIF and InfiniBand standards, which dovetail with IEEE standards.

#### REFERENCES

- 1. IEEE P802.3ak 10GBASE-CX4, https://www.ieee802.org/3/ak/index.html.

- 2. IEEE Std 802.3ap-2007, IEEE P802.3ap Backplane Ethernet, https://www. ieee802.org/3/ap/index.html.

- IEEE Std 802.3ba-2010, IEEE P802.3ba 40Gb/s and 100Gb/s Ethernet, https://www.ieee802.org/3/ba/index.html.

- IEEE Std 802.3bj-2014,100 Gb/s Backplane and Copper Cable, https:// www.ieee802.org/3/bj/index.html.

- J. Salz, "Digital transmission over cross-coupled linear channels," *Technical Journal*, July–August 1985, 64 (6), pp.1147–59.

Bibcode:1985ATTTJ..64.1147S. doi:10.1002/j.1538-7305.1985.tb00269.x.

S2CID 10769003.

- 6. C. Moore and A. Healey, "A Method for Evaluating Channels," *IEEE802.3* 100 Gb/s Backplane Copper Study Group, Singapore, March 2011.

- R. Mellitz, A. Ran, W. Bliss, W. Katz, and P. Patel, "Consensus Building Group Report Channel Analysis Method for 802.3bj Qualification and Specification," *100 Gb/s Backplane and Copper Cable Task Force*, May 2012, Interim Meeting, Minneapolis, Minn., https://www.ieee802.org/3/bj/public/ may12/diminico\_02a\_0512.pdf.

- A. Ran and R. Mellitz, "Analysis of Contributed Channels using the COM Method," 100 Gb/s Backplane and Copper Cable Task Force, July 2012, San Diego Calif., https://www.ieee802.org/3/bj/public/jul12/ran\_01a\_0712. pdf.

- R. Mellitz, C. Moore, M. Dudek, M. P. Li, and A. Ran, "Time-Domain Channel Specification: Proposal for Backplane Channel Characteristic Sections," 100 Gb/s Backplane and Copper Cable Task Force Plenary, July 2012, San Diego Calif., https://www.ieee802.org/3/bj/public/jul12/mellitz\_01\_0712.pdf.

- 10. IEEE Std 802.3bm-2015, 40 Gb/s and 100 Gb/s Fibre Optic, https://www. ieee802.org/3/bm/index.html.

- 11. IEEE Std 802.3by-2016, 25 Gb/s Ethernet, https://www.ieee802.org/3/by/ index.html.

- 12. IEEE Std 802.3bs-2017, 200 Gb/s and 400 Gb/s Ethernet, https://www. ieee802.org/3/bs/index.html.

- 13. IEEE Std 802.3cd-2018, 50 Gb/s, 100 Gb/s, and 200 Gb/s Ethernet, https://www.ieee802.org/3/cd/index.html.

- 14. IEEE Std 802.3ck-2022, 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces, https://www.ieee802.org/3/ck/index.html.

- 15. IEEE Std 802.3df-2024, 400 Gb/s and 800 Gb/s Ethernet, https://www. ieee802.org/3/df/index.html.

- 16. IEEE P802.3dj IEEE P802.3dj 200 Gb/s, 400 Gb/s, 800 Gb/s, and 1.6 Tb/s Ethernet Task Force, https://www.ieee802.org/3/dj/index.html.

**Richard Mellitz** is presently a Distinguished Engineer at Samtec, supporting interconnect signal integrity and industry standards. Richard has been a key contributor to IEEE802.3 electrical standards for many years. He led efforts to develop radically new IEEE and OIF time domain specification methods called COM and Effective Return Loss. Early in his career, he founded and chaired an IPC committee authoring the industry's first TDR standard. Richard holds many patents in interconnect, signal integrity, design, and test. Richard received the IEEE Standards Association Medallion and the Intel Achievement Award for spearheading the industry's first graduate signal integrity programs at the University of South Carolina. Richard was also honored with the DesignCon 2022 Engineer of the Year Award.

# YOU CAN'T BUILD AI WITHOUT POWER

# Transient Load Board Supporting 2000 Amps / ns It's just the beginning!

PICOTEST

New and innovative transient step load solutions combining user-software control and GaN to tackle sub 10uOhms power rail testing.

Hyper-fast 11-bit, 50MSPS kAmp loads for TDP, crosstalk, dynamic large-signal response testing, and impedance measurement of uOhm PDNs.

# -We Supply-

VNAs, Probes, Injectors, Steppers, TDR, Ground Isolators, Training. Transient Step Load, Impedance, Stability, PSRR, Part Modeling. Power Supply and Power Integrity Testing.

AVAILABLE

NOW

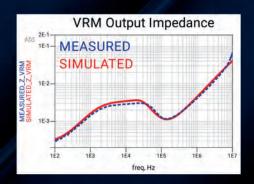

# Ultrafast Impedance Measurement of Active Ultra-High Current PDNs

Steve Sandler, Picotest

mpedance has always been the foundation of power integrity. Target Impedance, presented by Larry Smith, provided an intuitive design tool for engineers to determine impedance and expected dynamic voltage noise. "Target Impedance Limitations and Rogue Wave Assessments on PDN Performance" was presented at DesignCon 2015, showing that this relationship was not quite so simple unless the impedance was also flat. At the time,  $1 \text{ m}\Omega$  impedance was considered very low.

"How to Measure Ultra-Low Impedance (100uOhm and Lower) PDNs" was presented at EDI CON University in 2018. The presentation concluded with the mathematical relationships in ultra-low impedance measurements, determining the major obstacles and the mathematical solutions.

$$V_{measured} = 0.223 \cdot \sqrt{e^{0.2306 \cdot dBm}} \cdot \left[ \frac{DUT}{DUT + \frac{R_{port}}{2}} + \frac{1}{CMRR} \cdot \frac{R_{shield_{-1}}}{R_{shield_{-1}} + R_{port}} + \frac{1}{10^{\frac{Noise_{s}}{20}}} \right] + \frac{PDN_{voise}}{Error (Noise)}$$

(1)

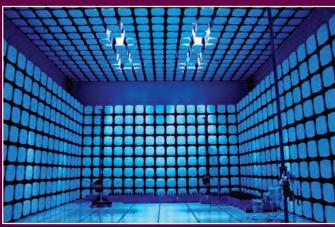

The increased core current for the latest AI, data center, and super computing segments made this measurement a lot more complicated, with power distribution network (PDN) impedance now as low as 10  $\mu$ Ω. Performing this measurement is a challenge, but it is far more difficult than simply performing the measurement. Many, if not most, new boards are liquid-cooled. While some are just refrigerated liquid, others are refrigerated and immersion cooled. Setting up this cooling is not trivial, and some joke that as a power integrity engineer in today's environment, one needs to be educated in plumbing. Due to this complexity, it would be much more desirable to perform the measurement without cooling, requiring that the measurement be

performed very quickly.

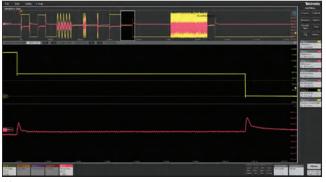

There is an additional challenge: while many are accustomed to measuring small signal impedance with a vector network analyzer (VNA), at these higher currents, there are large signal effects. The impedance is not constant but has a nonlinear load dependency. This is evident in the step load test results shown in **Figure 1**. The load is stepped from 1500 to 750 A and then from 750 to 0 A. Despite the current change being 750 A in both cases, the voltage excursions are notably different, both in response amplitude and in recovery time.

Therefore, three challenges are presented: how to measure either the small signal response or the large signal response; how to do so extremely quickly so it does not overheat without the attached cooling system; and how to do so for a 10  $\mu\Omega$  active PDN. This article will provide a few viable options, each of which can be performed using the same equipment.

The path here is to use a sophisticated and novel Fast Fourier Transform (FFT) based 3-port measurement (V/I). This method involves applying digitally modulated patterns to create modulated load currents up to 1500 A and recording the resulting power rail voltage perturbations.

▲ Fig. 1 The load is stepped from 1500 to 750 A and then from 750 to 0 A; note the asymmetrical responses. Other more complex step load patterns can be discerned in the upper gray areas.

#### (Re)Establishing the Issues

The final equation in the university paper referenced previously provided the mathematical description of the measurement and the limitations. This compact equation showed that the low frequency ground loop error is the result of the cable shield resistance and the isolator Common Mode Rejection Ratio (CMRR). The equation also included external PDN noise and the measurement noise floor. The theory is proven at the end of this presentation with the measurement of a 20  $\mu\Omega$  resistor.

Despite the appearance that a solution already exists, there are a few shortcomings, one being that this measurement is of a passive resistor. Active power supplies are not quiet; in fact, they can be quite noisy. Equation 1 included noise as a term that has been ignored thus far. The equation indicates requirements of 10  $\mu\Omega$ , so for the future, one needs a plan for measuring well below that.

Using Equation 1, the CMRR required for the measurement is solved as a percent error. In the case of a probe, the ground pin resistance is added to the shield ground in the numerator. The device under test (DUT) magnitude and percent error are in the denominator. Together, these establish the required CMRR.

$$CMRR = 20 \cdot \log \left[ \frac{Rcable + Rpin}{DUT \cdot Error\%} \right]$$

(2)

The P2102A 2-port probe from the article is then used as an example to measure a 10  $\mu\Omega$  DUT with an uncorrected error of 10%:

$$CMRR = 20 \cdot \log\left[\frac{30 \, m\Omega}{10 \, \mu\Omega \cdot 10\%}\right] = 89.5 \, dB \tag{3}$$

This is within the CMRR of the J2114A isolator shown in the article, so theoretically this measurement can be accomplished. However, at this point, one encounters the limitations caused by the power supply noise.

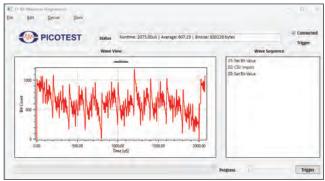

With the caveat that all power rails and voltage regulator models (Vrms) are different, and Constant-On-Time (COT and all derivatives) are noisier than pulse width modulation (PWM) Vrms, Figure 2 shows the power rail noise of the 1500 A ICONIC demo board (PWM).

$\bigstar$  Fig. 2 The measurement of a 20  $\mu\Omega$  resistor using a VNA in the 2-port shunt-through configuration.

Figure 3 shows the noise density to be in the range of -80 dBm. Using the 2-port shunt-through impedance measurement configuration, the attenuation of the signal, S21, is expressed as:

$$S21 = \frac{DUT}{DUT + 25} \tag{4}$$

At 10  $\mu\Omega$ , this is

$$S21 = 20 \cdot \log\left[\frac{10 \, u\Omega}{10 \, \mu\Omega \cdot 25 \, \Omega}\right] = -128 \, dB \tag{5}$$

This establishes the source power required for the measurement. Using the noise floor of -80 dBm and the signal attenuation of 128 dB:

Source\_dBm = noise\_floor + S21 and SourcedBm = (6) -80 dBm + 128 dB = 48 dBm

To be fair, the signal-to-noise ratio (SNR) requires the signal to be at least 6 to 10 dB above this for a decent measurement. Therefore, the minimum will be set at 54 dBm.

Using the Bode 100 VNA (which has a relatively high source power of +13 dBm) in combination with the B-AMP 12 amplifier adds 12 dB gain, resulting in 25 dBm, almost 30 dB short.

How much is 54 dBm?

$$Vrms(dBm) = 0.223 \cdot e^{0.23026 \cdot dBm}$$

(7)

This requires a 110 Vrms source signal to overcome the noise. Alternatively, the power plane noise of -80 dBm is 22 µVrms. A minimum 6 dB SNR requires a minimum of 44 µVrms to be applied to the DUT. This results in a signal current of:

Signal<sub>current</sub> =

$$\frac{44 \ \mu Vrms}{DUT}$$

=  $\frac{44 \ u Vrms}{10 \ \mu \Omega}$  = 4.4 Arms (8)

The 4.4 Arms signal, multiplied by the Thevenin 25  $\Omega$ , results in 110 Vrms, confirming the initial solution.

One could consider developing a 40 dB amplifier, but considering the voltage-related dangers to both the user and to the instruments, this is not a viable solution. While the Bode 100 is fast, measuring with a low receiver bandwidth to minimize the noise is not nearly fast enough to perform this testing without including the refrigeration cooling.

Fig. 3 Time domain and spectrum views of the power rail noise for the 1500 A ICONIC demo board.

## **Establishing Boundaries**

A few ground rules are required before actually defining the measurement solutions. For the purpose of this investigation, use the following conditions:

1. Let the maximum measurement acquisition time of 10 milliseconds (ms) be set arbitrarily. This is generally well within the limits of the Vrms on the power board and the load.

2. The measurement cannot require equipment other than typical validation equipment already commonly available.

The frequency range of the impedance measurement is from 1 to 2 kHz to a few MHz.

Additional post-processing time is allowed; the 10 ms restriction pertains to running a powered board up to and including its maximum load.

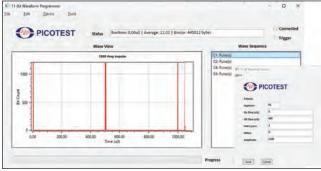

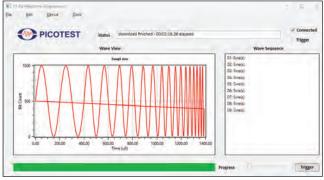

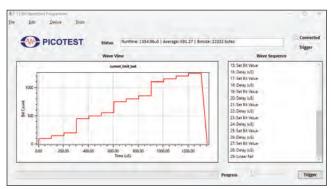

Since most high-power labs use some form of an in-socket load to validate the Vrm performance, this is the tool of choice. Here, a Picotest S2000 high-speed, in-socket, load board solution is used, but devices from other manufacturers should work similarly. The load board is a software-controlled load capable of emulating almost any current profile including pulses, sine waves, and pseudorandom patterns.

With the ground rules established, and after careful consideration, three load current modulation patterns were identified as candidates for this impedance measurement. The Picotest 1500 A ICONIC demo board was selected to power the S2000 load board, since it is very low impedance at about 30  $\mu\Omega$  and is easy to program the different waveforms. Any suitable board and load should be able to perform similarly.

An added benefit of using the load is that minimal current flows in the instrument cables. While this is a small

ground loop,

current is lim-

ited to the loop

through the load

most of the

▲ Fig. 4 A picture of the ICONIC demo board with the P2104A 1-port browser probe as well as the Tektronix MSO6B scope with a TPR4000 power rail probe in the background. A second cable is monitoring the programmed load pattern. and power board. Despite this, a TPR4000 power rail probe with a J2115A coaxial isolator and a P2104A browser tip to connect to the board were used (see **Figure 4**).

The three candidate methods for making this measurement are shown next, with a basic description and commentary in **Table 1**.

## Impulse

The impulse is well-known to have a flat response, or constant amplitude versus frequency, and wide bandwidth. The amplitude at each frequency is set by the pulse amplitude and the pulse duty cycle. The bandwidth is set by the on-time and the impulse repetition frequency, while the minimum frequency and the frequency spacing are set by the impulse repetition rate. This necessitates some compromises to achieve all the goals.

For this example, two sequential double pulses were used. The first two pulses are 1200 A, 5 microseconds (µs) wide and a 500 µs period. The duty cycle is 1%, resulting in an average power less than 10 W. The 5 µs pulse width results in a 3 dB bandwidth less than 100 kHz, which is short of the 1 MHz minimum goal. A second double-pulse is set for a 50 µs period and a 500 ns pulse increasing the bandwidth by an order of magnitude. This also averages less than 10 W. The entire acquisition requires a bit more than 1 ms memory allowing a 2 ms acquisition to capture 1 kHz. A third doublepulse could increase the maximum frequency. The S2000 software interface, showing the double-pulse program, is shown in **Figure 5**.

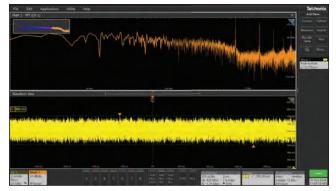

Two separate FFTs are performed after the voltage data is captured: one for the lower frequency pulse pair and one for the higher frequency pulse pair. The raw FFT results are shown in **Figure 6**. The impedance at each frequency is interpreted from the division of the voltage/current.

The impulse is the simplest measurement, requiring only a single level pulse. Achieving a reasonable amplitude requires large duty cycles, reducing the bandwidth. This is overcome by cascading several double pulses and extracting the FFT from each

|                  | TABLE 1           SUMMARY OF THE THREE CANDIDATES FOR LOAD CURRENT           MODULATION SOLUTIONS FOR THIS 3-PORT V/I MEASUREMENT |                                                                                                                                                  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Method           | Description                                                                                                                       | Comments                                                                                                                                         |  |  |  |  |  |  |  |

| Multi-impulse    | 4-6 low duty cycle single<br>amplitude pulses.                                                                                    | This method, being only one level, is also suited to stepper probes.                                                                             |  |  |  |  |  |  |  |

| Stepped sine     | Multiple sequential sine waves<br>at different frequencies.                                                                       | Requires high sample rate and many<br>levels.<br>The slowest and requires the most<br>post-processing, but also presents the<br>largest signals. |  |  |  |  |  |  |  |

| Compact-discrete | Many sine signals added<br>together for simultaneous<br>measurement.                                                              | Requires high sample rate and many<br>levels.                                                                                                    |  |  |  |  |  |  |  |

# HIGH-SPEED SIGNAL ANALYSIS Without Compromise

Our new **QCA Series digital sampling oscilloscopes** deliver powerful, cost-effective performance and exceptional measurement accuracy demanded by today's leading engineers.

- High-quality precision timebase and ultra-low jitter, comparable to industry leading performance.

- Easy-to-use VISEYE<sup>™</sup> jitter measurement and eye diagram analysis software.

- Supports 56 GBaud NRZ and PAM4 signals.

- Pair with the QCR Series clock recovery

instrument for optimum measurement accuracy.

- Scalable solution for high-speed interconnects, high-density ASICs, and AI processing ICs.

# JITTER MATTERS!

Learn why at quantifiphotonics.com/jitter

# ∑ VISEYE™

QCR

1

(0)

(0)

QUANTIFI PHOTONICS<sup>®</sup>

## TECHNICAL FEATURE

A Fig. 6 Raw FFT results of the lower frequency pulse pair and the calculated impedance from the extraction shows 26.2  $\mu\Omega$ .

double-pulse waveform, extending the bandwidth. The post-processing of the FFT data is relatively straightforward from the oscilloscope data, either internally or externally, and it is the lowest average power of all the solutions.

# **Swept or Stepped Sine**

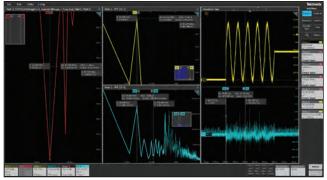

At the opposite extreme, the swept sine methodology is the slowest of the methods and requires the most post-processing, but also offers the largest signals, allowing measurement of the lowest impedance. Due to the very high sample rate of the controller, insufficient memory was available for the 11-bit sine signal at 1 kHz. This method in any case is included, since the controller sample rate will be made selectable to eliminate this limitation. This example includes nine sequential sine waves starting at 5 kHz and requiring 1.4 ms of run time (see **Figure 7**). At 1 kHz minimum, this would increase to 7 ms. Since higher frequencies will be required, the time will increase, but not significantly, and it will still easily meet the 10 ms criteria.

This example uses nine independent FFTs to demonstrate the first decade of frequencies, though the frequencies are known. Increasing the maximum frequency will increase this to approximately 30 FFTs within the scope. For the purposes of brevity, only one of the raw FFT results (7.5 kHz) is shown in **Figure 8**. The impedance at each frequency is interpreted from the division of the voltage/current.

The stepped sine is the most complex measurement because of the many individual FFTs required;

▲ Fig. 7 The S2000 controller software panel showing the nine sequential sine waves. Each consists of two cycles, and each is a 500 A peak with a 500 A offset for a 0 to 1000 A sine wave.

▲ Fig. 8 This method results in the largest signal, 344 A rms at 7.5 kHz is shown here. Two cycles are used at each frequency to obtain an FFT result.

however, this should be simple to automate with each frequency known. As it is all post-processed, the power board is not running aside from the 10 ms of allotted acquisition time. This measurement allows the largest of the signals, but has an average power of 250 W for the measurement duration.

# **Compact-Discrete Multi-Sine**

The third and final candidate is the compactdiscrete signal, which is in the class of multi-sine signals. As its name suggests, the single waveform is a complex sum of coherent, non-coincident, discrete sine waves. It has the benefit that it can excite many discrete frequencies with flat response. The signals are larger than the impulse, but this solution requires a high sample rate, high-resolution controller, and load. The process for determining the waveform is highly complex, but it is a built-in selection in the S2000 software controller, or it can be imported from an external CSV file. The GUI panel showing the CSV imported compact-discrete signal is shown in **Figure 9**.

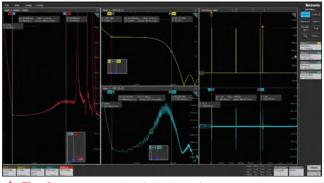

Like the stepped sine, this solution requires many FFTs; however, this method offers simultaneous FFT acquisition, and the FFT frequencies are known such as in the stepped sine solution, making the post-processing simpler. The maximum signal amplitudes are larger than the impulse and smaller than the stepped sine (see **Figure 10**).

LOS ANGELES *Since 1992* www.OphirRF.com

## TECHNICAL FEATURE

▲ Fig. 9 This compact-discrete signal was imported from a CSV file, but is also available from the pull-down menu for wave segments.

▲ Fig. 10 Raw FFT data from the compact multi-signal pattern on the lower right, and the voltage response on the upper right. The equal amplitude current signals are shown in the lower left with a 45 dBm amplitude. The extract impedance is 29  $\mu$ Ω.

# **DC Load Line for Comparison**

For reference, the resistance was also measured from the load line as the difference in voltage divided by the difference in current. This results in 42.4 milli-V/1500 A or 28  $\mu\Omega$  (see **Figure 11**). The division from the rms voltage and current between the cursors is a slightly higher 15.62 milli-V/507.6 A or 30  $\mu\Omega$ . This is a simple and direct measurement, but is only a DC measurement.

The compact-discrete FFT shows the individual frequencies and the flat response, with each signal being approximately 45 dBm. The individual voltage response to each frequency is also shown here. Again, the high sample rate, high-resolution waveform does not allow reaching as low as 1 kHz, but, as with the stepped sine solution, allowing control of the sample rate in the signal generation panel will eliminate this issue. Since

the stepped sine solution requires two cycles of the lowest frequency signal, the measurement requires 2 ms acquisition time for a 1 kHz minimum frequency signal. The maximum frequency is set by the load edge speed and the sample rate of the controller. The load speed bandwidth on this board is approximately 40 MHz and the controller sample rate is 66

A Fig. 11 The load line was measured as the difference in voltage between 0 A and 1500 A, resulting in a load line resistance of 28  $\mu\Omega$ .

MSPS. Halving the controller sample rate would allow nearly full bandwidth with a 1 kHz signal, using the maximum available controller memory.

## Conclusions

In this article, three candidate solutions for measuring ultra-low impedance with a maximum of 10 ms were presented. The methods are compared in **Table 2**. Though all three methods have pros and cons, they are useful approaches to keep in mind, as each one may serve a purpose at some point in time. All the methods use the same test equipment and setup.

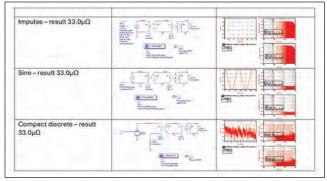

The methods are also compared in Pathwave ADS simulations, which eliminates the effects of noise, measurement errors, and other non-idealities. For this purpose, each signal was applied to a 33  $\mu\Omega$  resistor. The results are shown in **Figure 12** and all three were exactly 33.0  $\mu\Omega$ .

Each of these three methods meets the 10 ms measurement goal, even considering the sample rate change needed to allow longer acquisition windows. Any leftover time can be used to measure the power board efficiency, also without the cooling attached. With 100 µs dwell, the efficiency was measured at 13 discrete levels (see **Figure 13**).

In each case, the controller-programmed current (not the measured current) is multiplied by the output voltage, resulting in Equation 1. This product is divided by the product of the 48 V input voltage and the 48 V input current, which is Equation 2. The efficiency result, Equation 3, is shown in **Figure 14**. The required dwell time is set by the

| / | TABLE 2           THE RANKING OF THE THREE CANDIDATE OPTIONS FOR           THE KEY METRICS |                      |           |                     |                     |          |  |  |

|---|--------------------------------------------------------------------------------------------|----------------------|-----------|---------------------|---------------------|----------|--|--|

|   | Method                                                                                     | Signal<br>Complexity | Amplitude | Acquisition<br>Time | Post-<br>Processing | Measured |  |  |

|   | Multi-Impulse                                                                              | Low                  | Low       | Low                 | Low                 | 26.2 μΩ  |  |  |

|   | Stepped Sine                                                                               | Moderate             | High      | High                | High                | 33.6 μΩ  |  |  |

|   | Compact-<br>Discrete                                                                       | High                 | Moderate  | Moderate            | Moderate            | 29 μΩ    |  |  |

|   | Load Line                                                                                  | Low                  | High      | Low                 | None                | 28 μΩ    |  |  |

# Simulation vs Reality

# **Come see Siemens** @ DesignCon 2025

# Simulate what you actually build

What's the point in using advanced 3D EM modeling and simulation tools if what you build doesn't match what you simulated? That's a mistake designers make every day by using outdated analysis techniques. Close the gap between simulation and reality by ensuring that you simulate the design as built – efficiently, accurately and completely. Come see us to learn more about:

- Automated progressive verification

- Hyperscaler design & verification

- 3D IC design & verification

HyperLynx provides a complete family of scalable analysis solutions for electronic design and verification – for designs from small to state-of-theart and suitable for users from beginner to expert. No matter how simple or complex your analysis task, it's easier with HyperLynx!

## TECHNICAL FEATURE

**Fig. 12** All three methods are simulated using Keysight Technologies Pathwave ADS and provide the exact result of **33.0**  $\mu$ Ω.

A Fig. 13 Discrete current levels are set for measuring efficiency with a 100  $\mu$ s dwell. The measurement acquisition time is less than 1.5 ms.

▲ Fig. 14 The output current is stepped, and the input power and output power are monitored and divided to provide the efficiency data in a 1.5 ms acquisition without any cooling.

settling time of the input current. The overshoots in the efficiency curve are the results of the evaluation before the settling time and should not be used.

The total measurement acquisition time for the efficiency measurement is approximately 1.5 ms. Improvement in the quality of the measurement could be obtained by averaging a few measurement samples. Six samples could be performed in a 10 ms acquisition time, allowing the efficiency to be measured without attaching the cooling system. A special thanks to David Sandler. Without his help in developing this controller software and these waveform algorithms, none of this would be possible.

# **ACTUALIZE YOUR VISION**

Problems with SI/PI/EMC simulation, modeling, measurement, or ASIC packaging design?

# We deliver advanced SI/PI/EMC solutions.

From simulation to design to measurement success, we've got you covered with our selection of high-end services and products:

- Package Design: ASIC/Chiplet/MCM/SiP

- Interconnect Modeling: Die-to-Die and High-Speed SI/PI

- Electromagnetic (EM) Model Extractions

- Custom Measurement-Based Modeling

- IBIS Model Development

- Power Delivery Network (PDN) Modeling: State-Space Average VRM Models

- On-Site EMC Pre-Compliance Testing

- SI/PI/EMC Test and Measurement Solutions

# Simulations. Measurements. Modeling. Done Right.

CONTACT US

to find your solution www.signaledgesolutions.com

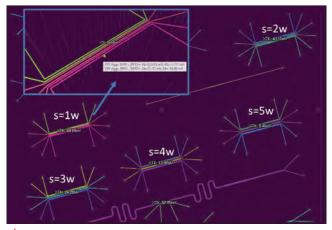

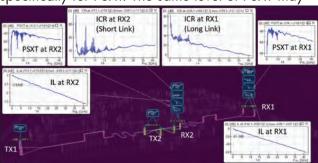

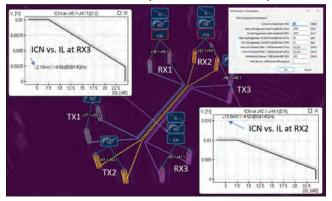

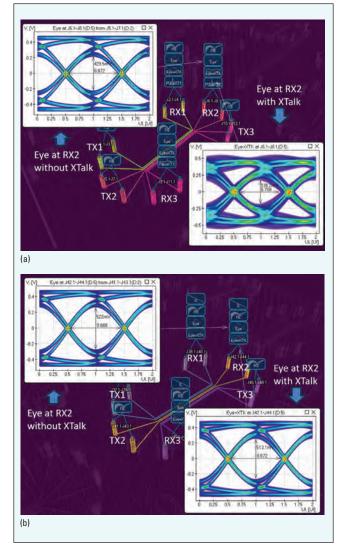

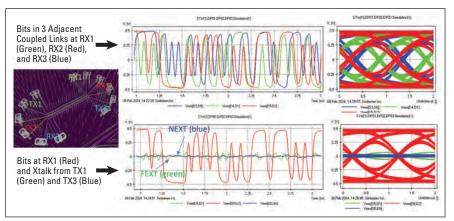

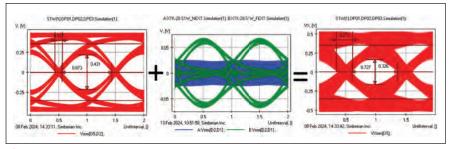

# How Interconnects Work: Crosstalk Quantification

Yuriy Shlepnev, Simberian Inc.

rosstalk is unwanted noise from structures coupled to a signal link that degrade the useful signal and may reduce the data transmission rate and even cause complete link failure. All possible signal degradation effects, including the crosstalk, can be expressed with the balance of power as follows:

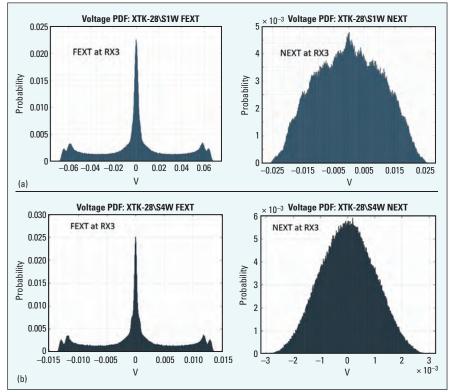

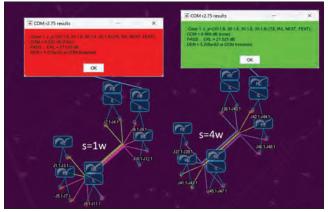

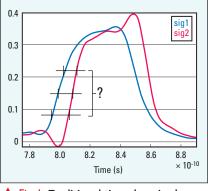

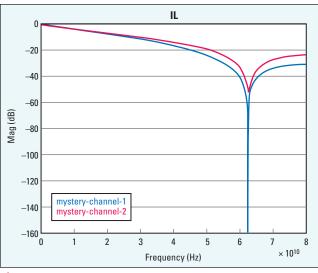

P\_out = P\_in - P\_absorbed - P\_ reflected - P\_leaked + P\_coupled